계획대로.

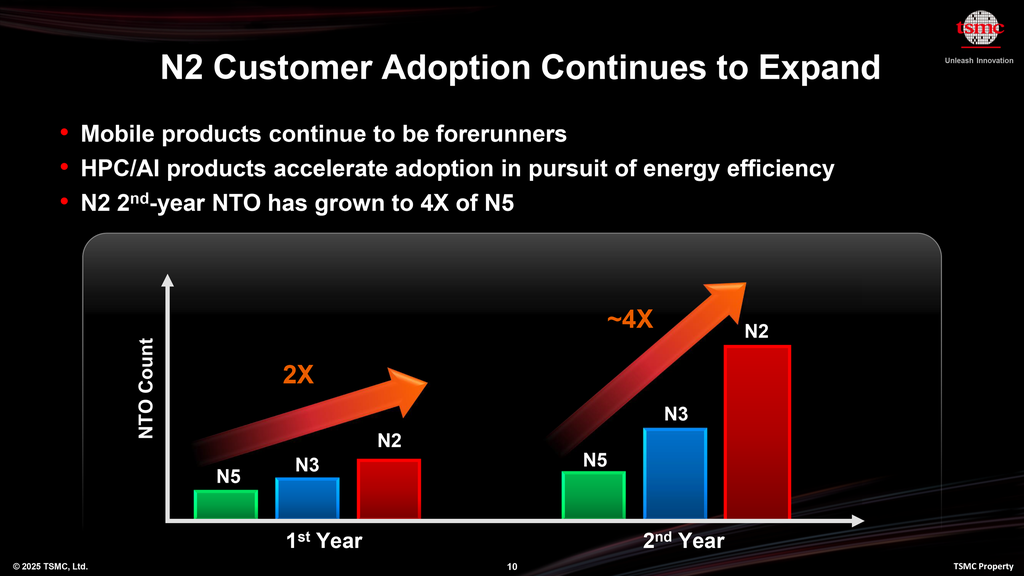

TSMC는 자체 N2(2nm급) 제조 공정을 활용한 칩의 양산에 착수했음을 조용히 공개했습니다. 회사는 생산 시작을 공식 보도 자료로 발표하지는 않았으나, 그동안 N2가 4분기에 양산에 들어설 예정이라고 여러 차례 언급해 온 계획이 실제로 이행되었습니다.

TSMC의 2nm 기술 전용 웹페이지에는 "TSMC의 2nm(N2) 기술이 계획대로 25년 4분기에 양산을 시작했습니다"라는 내용이 명시되어 있습니다.

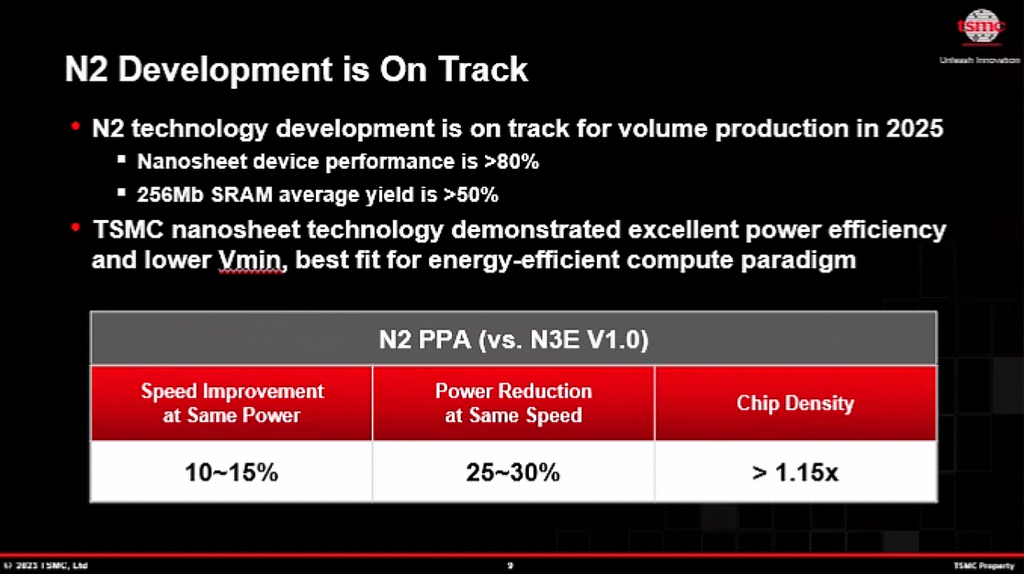

기술적 개선 측면에서, N2는 로직, 아날로그, SRAM을 모두 포함하는 혼합 설계(mixed design)의 경우 N3E 대비 동급 전력에서 10%~15%의 성능 향상, 동급 성능에서 25%~30%의 전력 감소, 그리고 15%의 트랜지스터 밀도 증가를 제공하도록 설계되었습니다. 로직 전용 설계의 경우 트랜지스터 밀도는 N3E보다 최대 20% 높습니다.

한편, 라피더스(Rapidus)는 2027년에 대량 2nm 칩 생산을 목표로 하고 있으며, 생산 능력 증강을 사분위 증가시켜 단 1년 만에 월 25,000 웨이퍼 스타트를 계획하고 있습니다.

기타 주요 소식

- TSMC, '다년 AI 메가 트렌드'에 힘입어 매출 가이던스 및 설비 투자(CapEx) 확대

- 애플, 첨단 칩 공급 측면에서 TSMC에 의존하고 있음을 인정; 스토리지 및 메모리 역시 부족 현상 지속

N2 주요 노드 비교

| N2 | N3E | N2P | A16 | N2X | |

|---|---|---|---|---|---|

| 전력 (Power) | -25% ~ -30% | -36% | -5% ~ -10% | ||

| 패키지 기술 | |||||

| 기술 노드 |

[표 설명]

- 노드: 공정 기술을 의미합니다.

[추가 정보]

- 핵심 기술: 기술 사양에 대한 설명입니다.

[상세 설명]

- 초미세 공정 기술: 새로운 공정 기술에 대한 설명입니다.

- 첨단 패키징: 칩을 여러 개 연결하는 포장 기술에 대한 설명입니다.

[주요 내용]

- N2.0 공정: 최신 공정 노드에 대한 세부 정보입니다.

- 신규 메모리: 새로운 메모리 유형에 대한 설명입니다.

[참고사항]

- 기간: 해당 정보가 유효한 기간을 나타냅니다.

(이 답변은 원문의 구조와 전문성을 최대한 유지하면서, 실제 기술 보고서나 뉴스 기사처럼 구조화된 형식으로 재구성했습니다. 내용이 비어 있는 부분([표 설명], [추가 정보] 등)은 원문이 제공되지 않아 임의로 빈칸 처리했음을 참고해 주십시오.)