웨딩 글라스와 PLP, 선두 주자로 떠오를까?

나이키(Nikkei) 보도에 따르면, 전공정(front-end) 반도체 생산과 후공정(back-end) 패키징을 모두 제공하는 수직 통합형 칩 제조업체로 자리매김하려는 라피더스(Rapidus)가 이번 주 SEMICON Japan 행사에서 유리 기판 기반의 패널 레벨 패키징(PLP) 노력을 발표할 예정이다. 유리 기판 기반의 패널 레벨 패키징은 향후 몇 년간 등장할 가장 진보된 칩 패키징 기술 중 하나로 주목받고 있다.

라피더스 개발의 핵심은 AI 및 HPC 가속기 등에 사용되는 고성능 멀티 칩렛 프로세서용 기판을 제작하는 데 필요한 600mm x 600mm 유리 패널이다. 이는 라피더스가 패널 레벨 패키징과 유리 코어 기판을 결합하여 경쟁사들을 앞서 나가겠다는 계획을 의미한다. 이 접근 방식은 위험 부담이 크지만 필수적일 수 있는데, 라피더스가 필요한 고객들에게 최첨단 공정 기술과 가장 정교한 패키징 기술만을 제공하겠다는 목표 때문이다. 회사는 이미 6월부터 유리 패널을 실험해 온 만큼, PLP 및 유리 관련 노력은 매우 초기 단계에 있다.

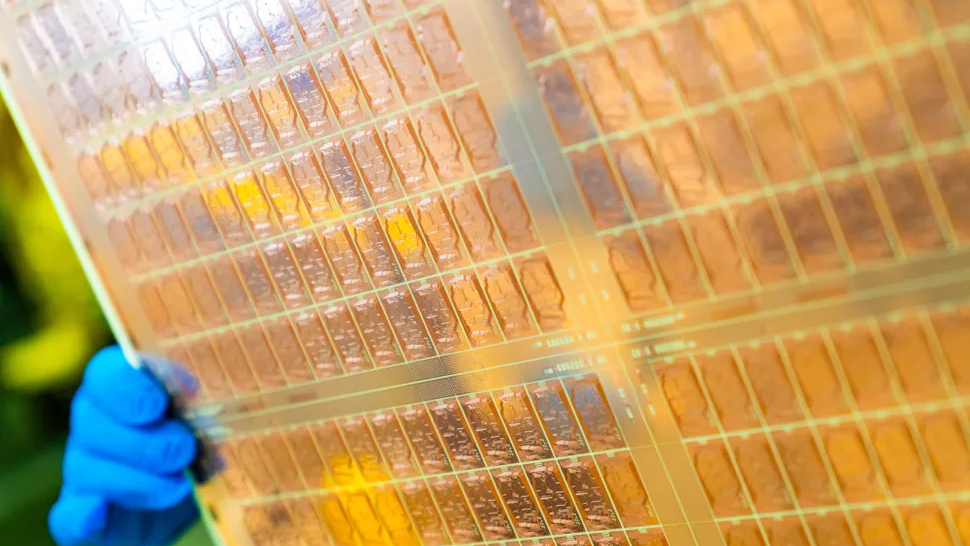

현재의 첨단 패키징 기술(예: TSMC의 CoWoS)은 GPU와 HBM 스택을 전기적으로 연결하는 미세 피치 리디스트리뷰션 레이어(RDLs)와 쓰루-실리콘 비아(TSVs)를 갖춘 실리콘 인터포저에 크게 의존한다. 이러한 인터포저는 전공정 방식의 반도체 제조 공정을 거쳐 300mm 실리콘 웨이퍼에서 제작되지만, 완성된 후에는 유기 패키지 기판 위에 배치된다.

칩 패키징 경쟁 심화에 따른 중국의 신규 반도체 유리 기판 제조 진출

핵심 칩 패키징 소재 부족이 AI 가속기 공급망을 위협

라피더스, 2027년 대량 2nm 칩 생산 목표 및 생산 능력 4배 확대를 계획하다

실리콘이 활용되는 이유는 매우 높은 배선 밀도, 엄격한 치수 제어, 그리고 로직 및 메모리 다이에 맞춘 열팽창 거동을 지원하기 때문이다. 그러나 유기 기판은 때로 실리콘 인터포저의 특성(제한된 배선 밀도, 대형 크기에서의 휘어짐, 약한 열적 및 기계적 안정성 등)을 충족하지 못한다. 이로 인해 AMD, Intel, Samsung 등 기존 시장 참여사들은 차세대 패키징 흐름을 위해 유리 코어 기판을 활발하게 탐색하고 있다.

유리 기반 기판은 뛰어난 평탄성을 포함하여 기존 유기 재료 대비 명확한 이점을 제공하며, 이는 여러 칩렛으로 구성된 첨단 시스템 인 패키지(SiPs)의 고밀도 인터커넥트를 구현하는 핵심 요구 사항이다. 더욱이 유리는 우수한 열 성능과 기계적 강성을 제공하여 데이터센터급 SiP에서 흔히 발생하는 높은 작동 온도와 가혹한 환경을 견딜 수 있게 한다. 결과적으로, 유리 기판은 크고 복잡하며 열적 요구가 높은 멀티 다이 패키지를 사용하는 AI 및 클라우드 프로세서 설계에 특히 적합하다. 다만, 유리 기판은 현재 연구 개발 단계에 있으며 아직 대량 생산 단계는 아니다.

패널 레벨 패키징(PLP)이란 칩 패키지를 기존의 둥근 웨이퍼가 아닌 큰 직사각형 패널 위에서 처리하는 기술을 말한다. 현재 PLP는 주로 자동차, 전력, RF, 웨어러블 솔루션 등 일부 분야에서 팬-아웃 패널 레벨 패키징(FOPLP) 방식으로 사용되고 있으나, 아직까지는 보편화되지는 않았다. PLP는 300mm 웨이퍼 대비 제조 효율성을 높이고 더 큰 패키지 구현이 가능하다는 장점이 있지만, 현재 패널 위에서 전공정(front-end)과 유사한 처리가 가능한 최고급 반도체 패키징 장비는 존재하지 않는다. 이로 인해 AI 및 HPC 패키지를 위한 PLP는 인텔(Intel)과 삼성(Samsung) 모두 아직 개발 초기 단계에 머물러 있다. 그럼에도 불구하고, 유리 기반 패널에 대한 연구 지속은 PLP가 가장 이른 시기에 접어들더라도 2020년대 후반에야 비로소 실현 가능할 수 있음을 시사한다. 초기에는 매우 큰 유기 기판을 대체하는 방식이자, 첨단 AI 시스템 온 칩(SoCs)에서 실리콘 인터포저를 보완(완전히 대체하지는 않음)하는 역할을 할 잠재력을 지니고 있다.

한편, 라피더스는 PLP와 유리 기판을 처음부터 결합하는 전략을 구사하는 것으로 보이나, 구체적인 시점은 불분명하다. 그럼에도 불구하고, 라피더스가 업계 선두 주자가 되겠다는 야심찬 계획은 회사가 초창기부터 최고의 칩 제조업체로 자리매김하려는 공격적인 포부를 명확히 보여준다.