14A 공정 기술의 기반을 마련합니다.

인텔은 상업용 칩 생산을 위해 개발된 업계 최초의 고수치 개구수(High-NA) 리소그래피 장비인 ASML의 Twinscan EXE:5200B를 설치했다고 발표했습니다. 이 장비는 승인 테스트를 성공적으로 마쳤으며, 인텔의 14A 제조 공정 개발에 사용될 예정입니다. 14A 공정은 가장 중요한 레이어에 고수치 개구수 EUV 스캐너를 의존하는 세계 최초의 노드가 될 것입니다. 이러한 성과는 고수치 개구수 EUV 리소그래피가 초기 실험 단계를 넘어 고대량 생산(HVM) 단계로 진입하고 있음을 시사합니다.

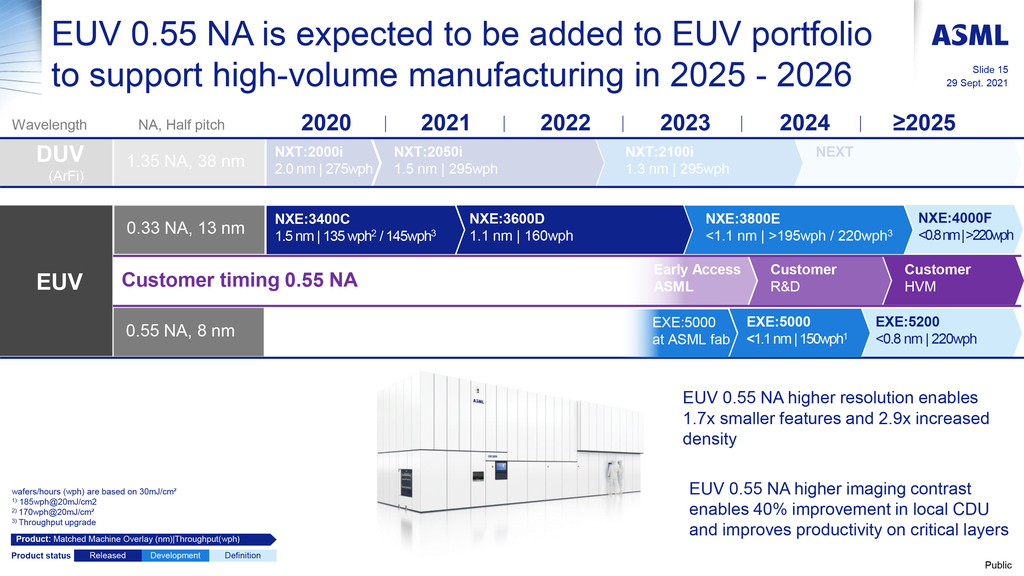

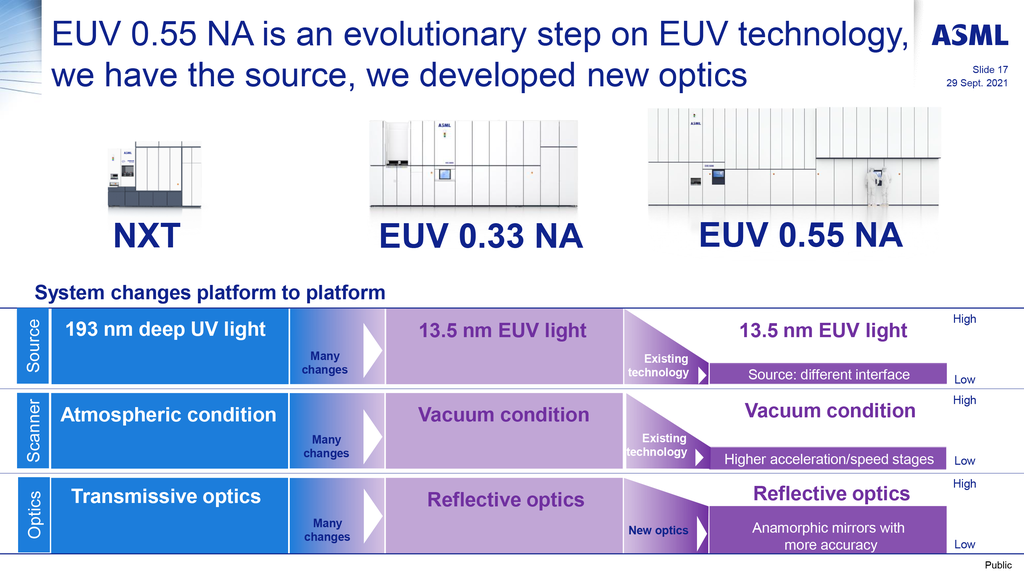

ASML의 Twinscan EXE:5200B는 인텔이 2023년 오리건 R&D 공장에 도입했던 1세대 EXE:5000 플랫폼을 기반으로 합니다. 신형 장비는 8nm 해상도로 칩을 '인쇄'할 수 있어, 현재 13nm 해상도를 제공하는 저수치 개구수(Low-NA) EUV 장비로는 불가능했던 차세대 스케일링을 가능하게 합니다. EXE:5000과 달리, EXE:5200B는 50 mJ/cm² 도즈에서 시간당 175개의 웨이퍼를 처리할 수 있습니다(20 mJ/cm² 도즈 시의 185개/시간 대비 개선). 또한, 구조 치수(feature dimensions)가 지속적으로 미세화됨에 따라 매우 중요한 매개변수인 오버레이 정확도(overlay accuracy) 0.7 나노미터를 달성했습니다.

성능 향상을 위해 이 스캐너는 고출력 EUV 광원을 통합하여 50 mJ/cm² 도즈에서도 더 빠른 웨이퍼 노출을 구현했습니다. 이는 현대 생산 노드에서 해결하기 까다로운 라인 에지 거칠기(LER) 및 라인 폭 거칠기(LWR)를 최소화하면서, 강력한 이미지 대비를 확보한 작업 가능한 레지스트/공정 창(resist/process windows)을 지원합니다.

ASML, EUV 칩 제조 기술에서 획기적 발전하며 2030년까지 속도 50% 증대 목표

인텔, 14A 공정에 대한 두 곳의 잠재 고객 확보

ASML과 인텔은 개발 범위를 광학계와 광원에만 국한하지 않았습니다. 웨이퍼가 스캐너에 저장, 대기, 투입 및 배출되는 전체 과정을 담당하는 웨이퍼 스토커 시스템(wafer stocker system)까지 재설계했습니다. 차세대 장비에서 이 시스템 구성 요소는 생산성 및 패턴 정확도 양쪽에 직접적인 영향을 미치기 때문입니다.

개선된 스토커 설계는 로트 흐름과 웨이퍼 취급 과정을 최적화하여 웨이퍼가 노출 단계에 보다 예측 가능한 상태로 도착하도록 보장합니다. 아울러, 노출 전후에 웨이퍼와 캐리어를 안정적인 온도로 유지하는 정밀한 열 제어(tighter thermal control) 기능을 제공합니다. 이는 극미세한 온도 변화만으로도 웨이퍼 팽창 또는 수축을 유발하여 오버레이 오류를 초래하고, 결국 결함 증가 및 수율 감소를 야기할 수 있으므로 매우 중요한 요소입니다.

나아가, 열적 및 기계적 변동성을 줄인 새로운 아키텍처는 장시간 가동 시 시스템 드리프트(drift)를 최소화하는 데 도움을 줍니다. 따라서 스캐너가 안정적인 동작 상태를 유지할 수 있어 잦은 재교정(recalibration)의 필요성을 낮춥니다. 이러한 안정성은 향후 몇 년간 1nm 이하 공정 기술에 필수적으로 적용될 다중 패스 및 다중 노출 패턴화 과정에서 특히 중요합니다.

EXE:5200B의 주요 성능 지표 중 과소평가할 수 없는 부분이 바로 0.7 nm에 달하는 오버레이 성능입니다. 이는 스테이지 제어, 센서 교정, 환경 격리 기술의 발전 덕분에 달성된 것입니다. 오버레이 성능은 아주 미세한 정렬 오차도 수율 손실로 직결될 수 있는 차세대 공정 기술에서 핵심적인 요소입니다.

ASML의 Twinscan EXE:5200B는 인텔 공장에 설치된 또 다른 EUV 스캐너와는 그 의미가 다릅니다. 이는 인텔이 반도체 산업 내 리더십을 회복할 수 있는 기반 시스템으로 기대받고 있습니다.

인텔이 이 새로운 리소그래피 장비를 활용하려면, 고수치 개구수 EUV 패터닝에서 최대 가치를 추출하기 위해 마스크, 식각 공정, 해상도 향상 기술, 측정 기술(metrology) 등 여러 영역에서 병렬적인 작업과 공동 최적화가 필수적입니다.

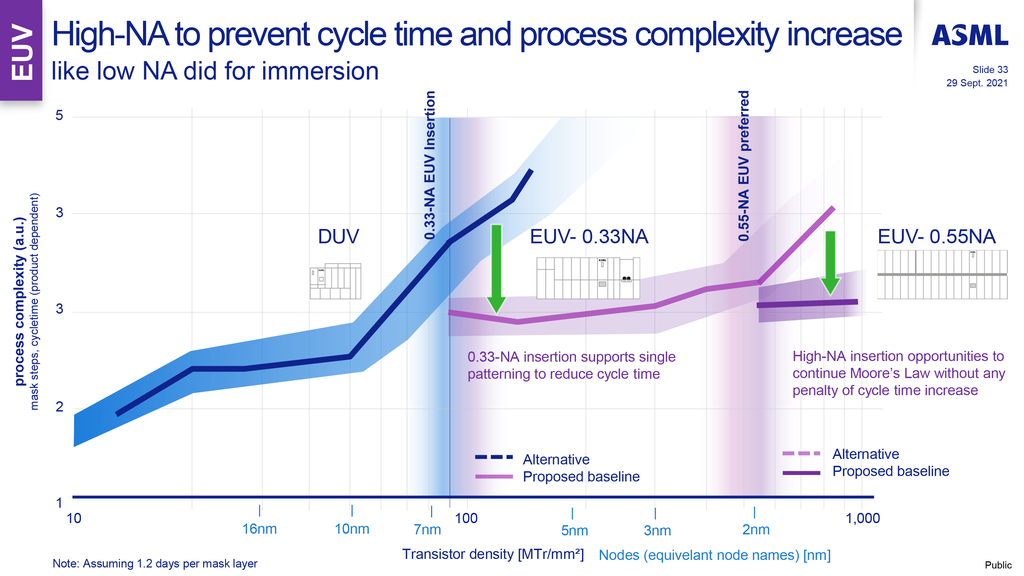

인텔에 따르면, High-NA 장비는 14A 및 그 이후의 발전된 공정 기술을 통해 멀티패터닝의 필요성을 줄여 더욱 유연한 설계 규칙을 구현하고, 패터닝 공정 단계를 감소시키며, 마스크 개수와 사이클 시간을 단축하고, 궁극적으로 수율을 향상시킬 수 있습니다. 동시에, 인텔이 High-NA EUV 장비 사용법과 귀중한 HVM(High Volume Manufacturing) 경험을 쌓는 과정에서, 수율에 큰 영향을 주지 않으면서 서브-1nm 시대에 필요할 때 High-NA EUV 멀티패터닝을 적용하는 역량을 갖추게 될 것입니다.

본 자료는 Tom's Hardware의 분석을 바탕으로 작성되었습니다.