느리지만 확실하게.

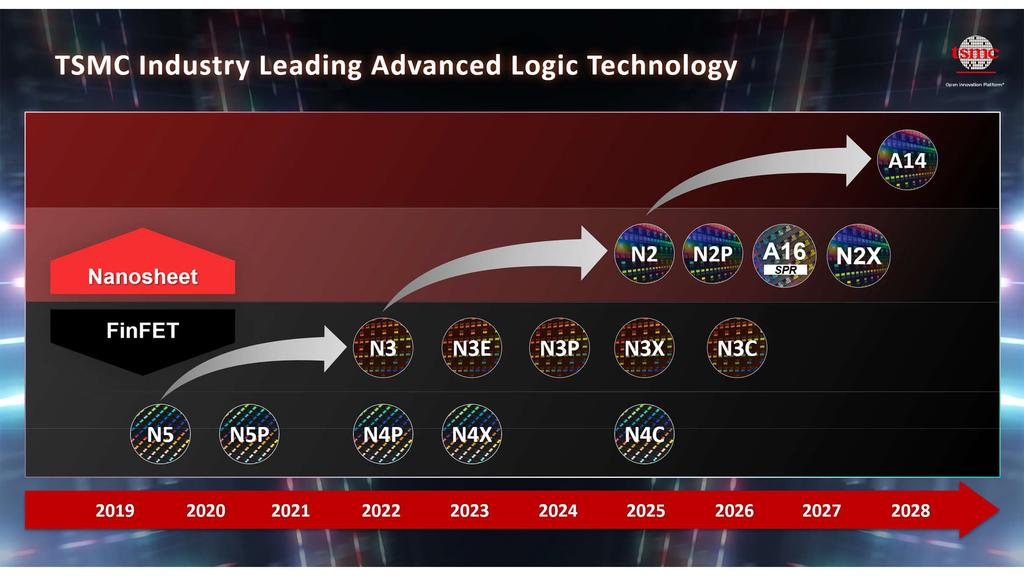

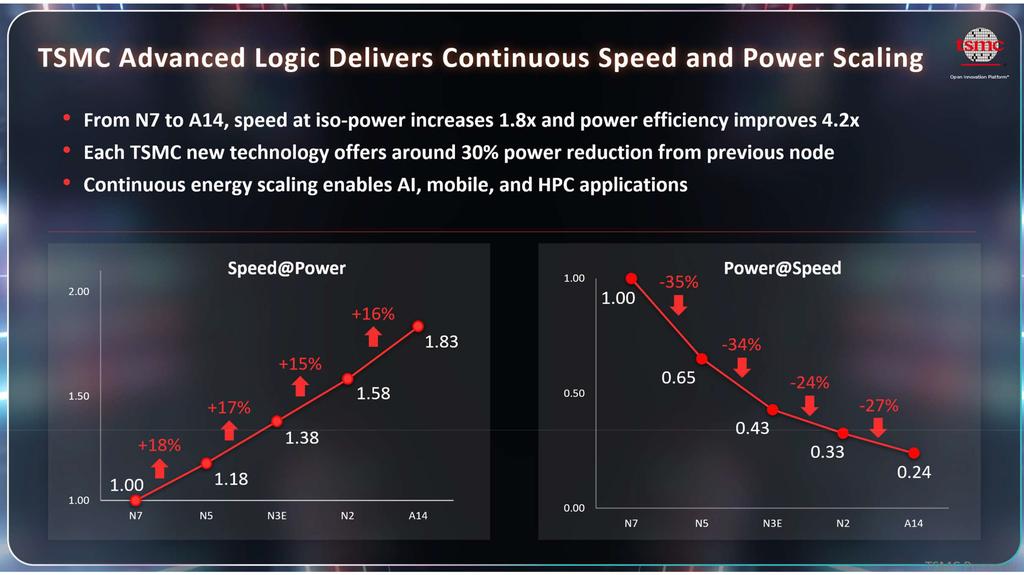

TSMC가 유럽 OIP 포럼에서 발표한 슬라이드는 2028년 출시 예정인 A14 (1.4nm급, 전면 측 전력 공급) 제조 공정이 직전 세대 공정 대비 제공할 장점을 명확히 보여줍니다. A14는 N2 (2nm급, 전면 측 전력 공급) 대비 같은 전력 및 복잡성에서 16% 더 높은 성능을, 같은 클럭 및 복잡성에서는 27% 낮은 전력을 제공하는 것으로 나타났습니다.

한편, 산업계에서는 여전히 설계된 목표 달성이 가능한지에 대한 의문이 제기되고 있습니다.

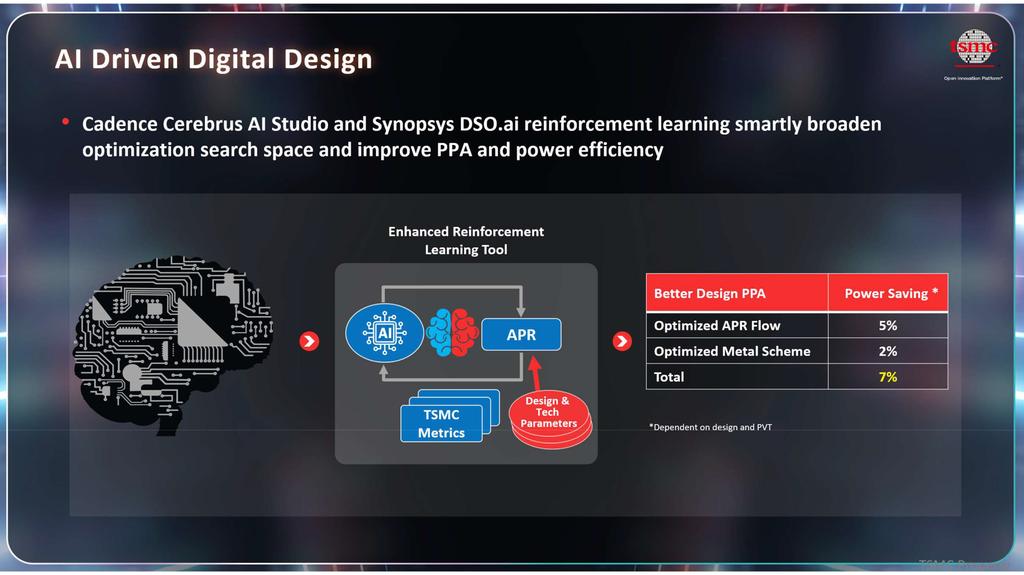

이러한 배경 속에서, 최근에 발표된 논문은 칩 디자인 과정에서 AI를 활용하는 새로운 방법을 제시하며, 설계된 목표 달성을 위한 새로운 길을 열어주었습니다.

이 연구는 칩 설계를 위해 최적의 전력 소비를 달성하는 방법을 제안하며, 기존의 설계 방식으로는 어려웠던 목표까지 달성할 수 있는 가능성을 보여주고 있습니다.

따라서, 해당 논문은 향후 반도체 설계 분야에 혁신적인 변화를 가져올 것으로 기대됩니다.

【원문 내용에 따른 수정 요청】

요청하신 원문 내용(기술 분석 및 논문 요약)을 반영하여, 전문성을 높이고 흐름이 자연스러운 기술 분석 보고서 형식으로 재구성했습니다.

[수정된 전문]

최근 반도체 설계 분야에서 전력 효율성 확보는 핵심 과제로 부상하고 있습니다. 한편, 학계에서는 이러한 설계 난제에 대응하기 위한 새로운 방법론을 제시하며 주목받고 있습니다.

최근 발표된 논문은 반도체 칩 디자인 과정 전반에 걸쳐 인공지능(AI)을 접목하는 혁신적인 접근 방식을 제안합니다. 이 연구의 핵심은, 칩 설계 목표 달성을 위해 필요한 최적화된 전력 소비 패턴을 도출하는 것입니다. 이는 기존의 설계 워크플로우만으로는 도달하기 어려웠던 까다로운 설계 목표를 달성할 수 있는 새로운 가능성을 제시합니다.

따라서 이 논문은 향후 반도체 설계 프로세스에 구조적인 개선을 가져올 것으로 기대되며, 해당 분야의 기술적 패러다임 전환을 예고하고 있습니다.