연구원들이 거의 제로의 패스 전압과 셀당 최대 5비트를 갖는 FeFET 기반 3D NAND 셀을 시연했습니다.

삼성 연구진은 NAND 기술의 주요 전력 소비원 중 하나를 최대 96%까지 절감하는 것을 목표로 하는 실험적인 NAND 아키텍처에 대한 상세 연구 결과를 발표했습니다.

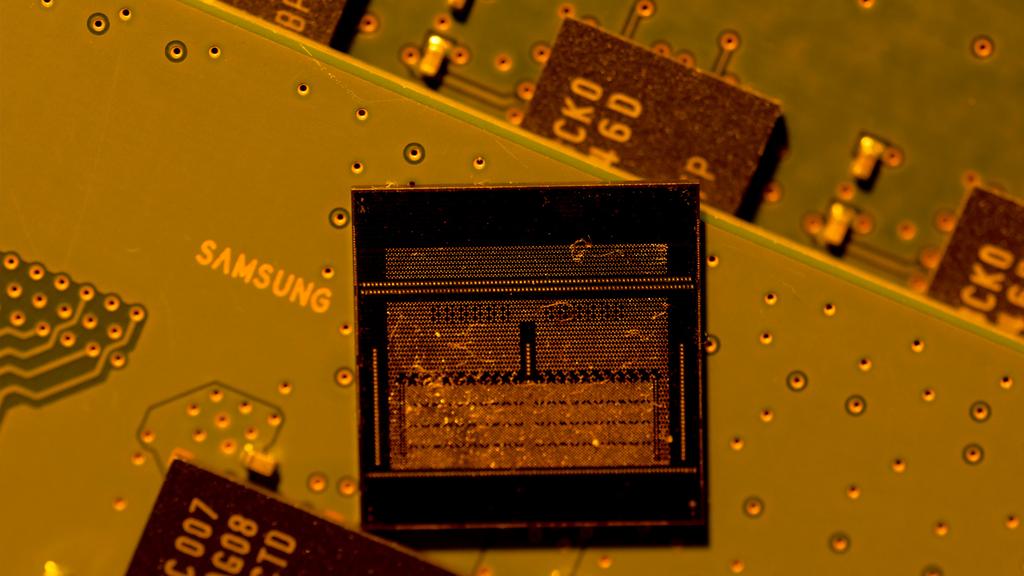

‘저전력 NAND 플래시 메모리를 위한 강유전체 트랜지스터(Ferroelectric transistor for low-power NAND flash memory)’라는 제목의 본 연구는 삼성전자 첨단기술연구센터(Samsung Advanced Institute of Technology) 연구진이 수행했으며, 학술지 네이처(Nature)에 게재되었습니다. 이 논문은 향후 3D NAND에 적용할 목적으로 설계된 강유전계효과 트랜지스터(FeFET) 구조를 설명하고 있습니다. 이 구조는 하프니아(hafnia) 기반의 강유전체와 산화물-반도체 채널을 결합하고, 거의 0V에 가까운 통과 전압(near-zero pass-voltage) 작동을 도입함으로써 96%의 전력 절감 수치를 제시합니다.

기존 NAND 플래시 메모리에서 각 수직 스트링을 통과하는 워드라인(wordlines) 스택은 셀을 읽거나 프로그래밍할 때마다 통과 전압(pass voltage)으로 바이어스 되어야 합니다. 레이어 수가 증가함에 따라 이러한 전력 오버헤드도 커지며, 이제는 전체 어레이 전력의 상당 부분을 차지하는 문제가 되었습니다. 삼성 연구진은 넓은 메모리 창(memory window)과 0V 이하로 낮춰진 최대 문턱 전압을 갖는 강유전체 트랜지스터가, 데이터 불안정성(disturb)을 방지하기 위해 기존 전하 트랩(charge-trap) NAND가 의존하는 높은 $V_{pass}$ 없이도 다중 레벨 동작을 지원할 수 있다고 주장합니다.

연구진은 이 개념을 먼저 최대 셀당 5비트까지 구현 가능한 평면 어레이(planar arrays)에서, 이후 3D NAND의 기하학적 구조를 모방하여 설계된 4층 수직 스트링에서 성공적으로 시연했습니다. 이 구조의 중앙 게이트는 현재 상업용 장치와 유사한 25나노미터(nanometres) 크기를 가집니다. 또한 연구진은 워드라인 커패시턴스와 읽기 및 쓰기 과정에서 높은 전압을 생성하는 내부 전하 펌프(internal charge pumps)가 기여하는 핵심 요소를 결합한, NAND 전용 에너지 측정 지표를 정의했습니다.

이러한 비용 구조를 전체 스택에 걸쳐 모델링한 결과, 연구진은 강유전체 설계 기반의 286층 장치가 동일한 높이의 기존 전하 트랩 스택과 비교했을 때, 프로그램 및 읽기 에너지 합계를 약 94%까지 줄일 수 있다고 추정했습니다. 특히 1,024층에 달하는 깊이에서는 통과 전압이 낮아지면서 전하 펌프가 소모하는 에너지가 급격히 감소하여 절감률이 96%를 초과합니다.

실험은 또한 리텐션(retention) 및 사이클링 한계 테스트도 수행했습니다. 평면 형태로 구현된 강유전체 셀은 넓은 메모리 창을 지원하며 5레벨 프로그래밍이 입증되었으나, 이 밀도에서의 내구성은 상대적으로 낮습니다. 성능 등급 측면에서, PLC 등급 구성은 수백 사이클을 유지하는 반면, QLC에 상응하는 사용은 상온 및 85°C 모두에서 약 1,000회까지 가능했습니다. 저자들은 완전한 3D 어레이가 실제 생산에 적용되기 위해서는 프로그램 방지(program-inhibit) 기법 및 음전압 생성 기술에 대한 추가 개발이 필수적이라고 강조했습니다. 아울러, 산화물 채널이 고온 스트레스 하에서 보이는 거동은 향후 연구가 필요한 핵심 영역으로 지적되었습니다.

현재로서는 삼성전자가 이 연구를 기반으로 한 구체적인 제품 발표 계획에 대한 어떠한 징후도 없습니다. 대신, 이 연구는 현재의 전하 트랩 로드맵을 초월하여 잠재적인 저전력 NAND 세대를 개발하기 위한 기반 연구(foundational research) 성격으로 다루어지고 있습니다.

(이하 내용은 본문과 무관한 출처 홍보 문구입니다.)