18A는 수율 상승 곡선 중간 지점입니다.

(전문적이고 자연스러운 기술 보고서 또는 기사 형식으로 다듬었습니다.)

인텔, 차세대 패키징 아키텍처와 생산 역량 강화에 박차

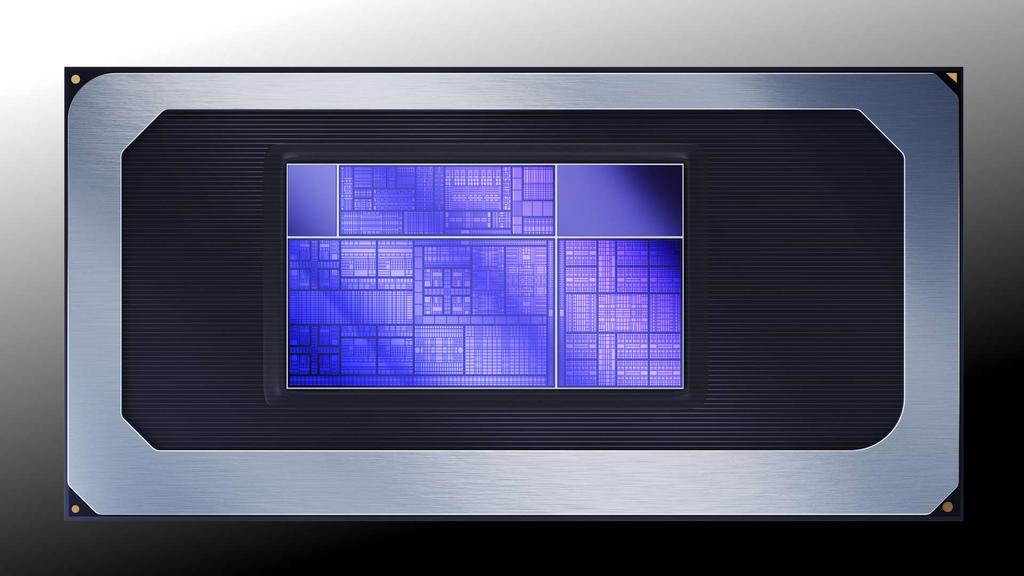

인텔은 최근 클라이언트 및 데이터센터 시장을 겨냥한 최신 패키징 아키텍처와 제조 역량 강화 계획을 발표하며 시장의 주목을 받고 있습니다. 이러한 발표는 인텔이 고성능 컴퓨팅(HPC) 시장에서 경쟁 우위를 점하고, 미래 반도체 패키징의 표준을 재정립하겠다는 의지를 명확히 보여줍니다.

애널리스트들은 이번 제품 로드맵을 통해 인텔이 향후 몇 분기 동안 점진적으로 시장에 제품을 출시할 것으로 예상하고 있습니다. 이는 특히 전력 효율성과 성능 밀도가 핵심 요구 사항인 최첨단 컴퓨팅 환경에 맞춰 설계된 것이 특징입니다.

획기적인 패키징 아키텍처 도입

인텔이 제시한 핵심 기술은 고성능 패키징 아키텍처의 도입입니다. 이는 단순히 프로세서의 성능 향상을 넘어, 시스템 전반의 전력 관리 및 입출력(I/O) 용량을 획기적으로 개선하는 데 초점을 맞추고 있습니다.

이러한 아키텍처 설계는 메모리, CPU, GPU 등 다양한 컴포넌트들을 단일 패키지 내에서 효율적으로 통합하는 ‘소켓리스(Socketless)’ 방식을 지향하며, 궁극적으로 전체 시스템의 전력 효율성(Power Efficiency)을 최적화하는 것을 목표로 합니다.

제조 공정 및 수율(Yield) 확보 전략

더불어 인텔은 차세대 제품의 상업적 성공을 위한 제조 공정 및 생산성 확보 전략을 함께 공개했습니다.

과거 반도체 제조에서 핵심 과제였던 ‘수율(Yield)’ 확보 문제를 해결하기 위해, 인텔은 공정 전반에 걸쳐 첨단 검사 장비(Inspection Equipment)를 대폭 투입하고 있습니다. 이는 웨이퍼 단계에서 발생하는 미세 결함을 극도로 높은 정확도로 감지하고 수정함으로써, 제품 출하량이 예상보다 크게 감소하는 사태를 방지하는 데 중점을 둡니다.

구체적으로, 인텔은 다음과 같은 핵심 개선 사항을 발표했습니다:

- 수율 예측 모델 고도화: AI 기반의 예측 모델을 도입하여, 수율 저하 요인을 사전에 진단하고 공정 파라미터를 실시간으로 조정할 수 있는 시스템을 구축했습니다.

- Fab 효율성 극대화: 제조 시설(Fab) 운영의 유연성을 높여, 특정 부품 라인에 병목 현상이 발생하더라도 전체 생산 라인의 가동률을 유지하도록 설계 변경을 완료했습니다.

시장 전망 및 기대 효과

이번 패키징 아키텍처와 제조 공정 최적화의 결합은 인텔 제품의 시장 경쟁력을 한 단계 끌어올릴 것으로 기대됩니다.

전문가들은 이러한 통합적인 접근 방식이 클라이언트(PC 및 노트북) 시장에서 높은 전력 효율성을 요구하는 사용자들에게 매력적인 선택지로 작용할 것이라 분석합니다. 또한 데이터센터 시장에서는 대규모 연산이 필수적인 AI 및 머신러닝 워크로드에서 안정적이고 예측 가능한 성능을 제공하며 시장 점유율을 확대하는 동력이 될 것으로 전망합니다.

요약하자면, 인텔은 단순한 프로세서 성능 개선을 넘어, 제품의 설계(아키텍처)와 생산(제조 공정)의 전 과정을 통합적으로 최적화함으로써 시장 요구사항에 가장 최적화된 반도체 솔루션을 제공하겠다는 강력한 의지를 보여주고 있습니다.