푸단 대학교 연구원들이 몇 개의 원자층 두께를 가진 작동 기억 칩을 개발했습니다.

과학자들은 2차원(2D) 물질을 사용하여 작동하는 메모리 칩을 처음으로 성공적으로 구축하고, 이를 기존 실리콘 다이에 직접 통합하는 획기적인 성과를 이루었습니다. 이 연구는 미래 반도체 제조 방식에 큰 변화를 가져올 수 있는 이정표로 평가받고 있습니다. 상하이 푸단대학교의 춘센 리우(Chunsen Liu)와 동료들이 주도한 이 연구 결과는 10월 9일 학술지 네이처(Nature)에 게재되었습니다.

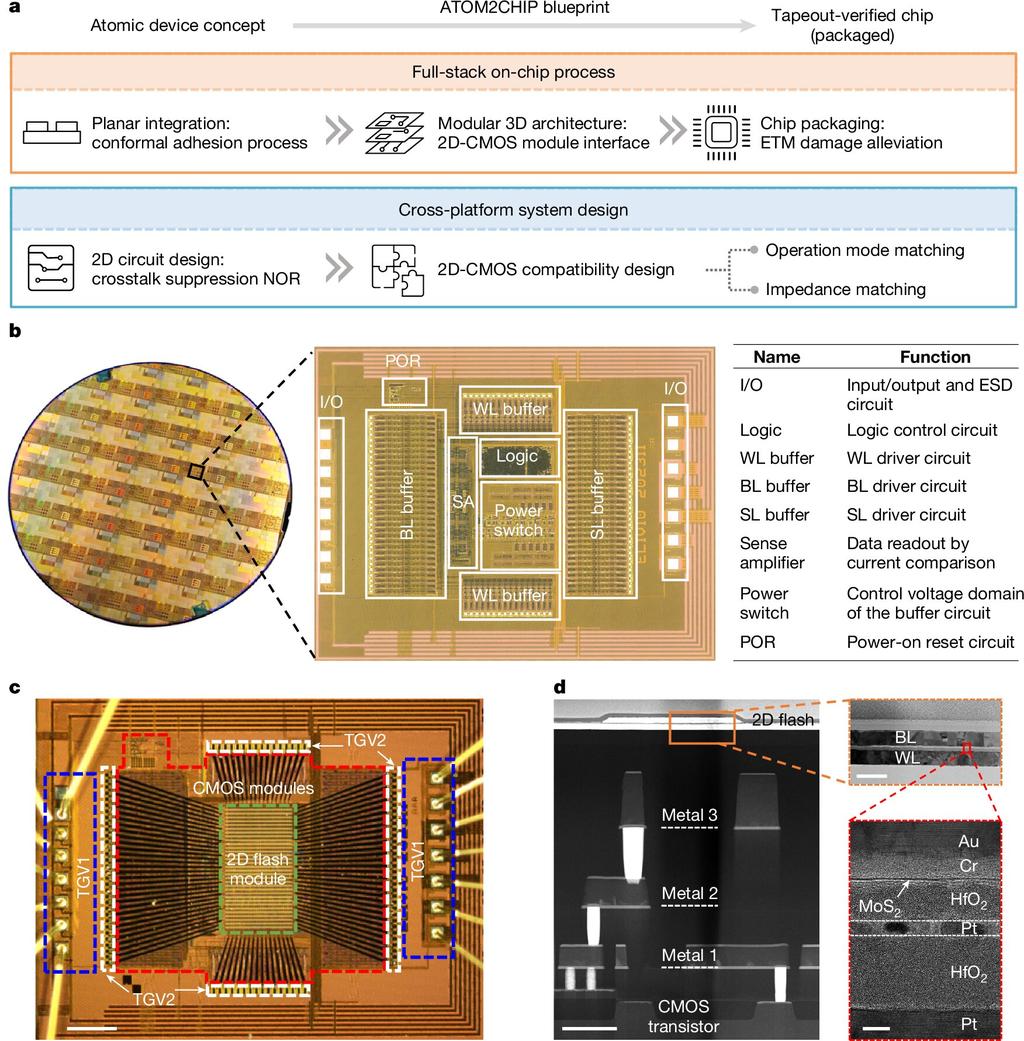

본 연구는 오랫동안 원자 단위의 성능과 효율성을 약속했지만, 실험실 수준의 시연을 넘어 상업화에 어려움을 겪어왔던 2D 전자공학 분야에 전환점이 될 가능성이 높습니다. 연구팀은 ATOM2CHIP이라 명명된 공정을 사용하여, 단 몇 개의 원자로 이루어진 황화 몰리브데넘(molybdenum disulfide) 층을 기존의 0.13마이크로미터(micrometer) CMOS 실리콘 칩 위에 직접 성장시키는 데 성공했습니다. 그 결과물은 2D NOR 플래시 메모리 어레이와 표준 CMOS 컨트롤러를 결합한 하이브리드 칩으로, 실험적인 나노물질과 산업 표준 공정 기술 간의 간극을 효과적으로 해소했습니다.

푸단팀은 전체 칩 테스트에서 94.34%라는 높은 수율을 보고했는데, 이는 상업용 실리콘 생산 결과에 견줄 만한 수치입니다. 또한, 최대 5메가헤르츠(MHz)의 작동 속도를 구현했으며, 각 비트당 소비 전력은 0.644 피코줄(pJ)에 불과하여 현존 실리콘 플래시 셀 대비 월등히 낮은 전력 소모를 보여줍니다. 이 메모리는 20나노초(nanosecond)의 빠른 프로그래밍 및 지우기 속도, 10년간의 데이터 보존 기간, 그리고 10만 회 이상의 쓰기 내구성 등 우수한 성능을 입증했습니다.

[연구자들은 프로세서에 직접 내장할 수 있는 원자층 두께의 2D 온도계를 만들었습니다.]

[차세대 고밀도 데이터 저장의 핵심은 비틀린(twisted) 2D 물질에서 발견되는 새로운 자기 상태일 수 있습니다.]

이러한 목표를 달성하기 위해 연구진은 표면 거칠기(surface roughness)라는 기술적 과제를 극복해야 했습니다. 실리콘 칩은 연마 과정을 거친 후에도 나노미터(nm) 규모에서 불균일한 지형을 가지고 있어, 원자층 두께의 물질에 손상을 주거나 스트레스를 가할 수 있습니다. ATOM2CHIP 방법은 2D 물질이 기저 회로의 윤곽을 따라 끊어지지 않고 "흐르도록" 하는 등방성(conformal) 접착 공정을 도입했으며, 2D 친화적인 패키징 시스템을 통해 열 및 정전기 손상으로부터 보호합니다.

이와 더불어, 팀의 "크로스 플랫폼 시스템 설계"가 핵심적이었습니다. 이 맞춤형 인터페이스는 2D 층이 CMOS 제어 논리 회로와 원활하게 통신할 수 있도록 보장합니다. 이 설계를 통해 명령 기반 작동, 32비트 병렬 처리, 무작위 액세스 등의 기능이 가능해지면서, 기능적으로 완전한 메모리 칩을 구현할 수 있었습니다.

저자들은 논문에서 이 성과를 "2D 전자공학의 우수성을 입증하는 이정표"로 평가했습니다. 이 기술은 차세대 컴퓨팅 분야에 중요한 함의를 가지며, 향후 전력 효율성이 극대화된 고성능 메모리 구현에 기여할 것으로 기대됩니다.

(참고: 마지막 문단은 원문의 의도에 따라 재구성되었으며, 전문적인 맥락에서 최종 결론을 제시하는 역할을 수행합니다.)